Output Characteristics of n-channel JFET

Procedure

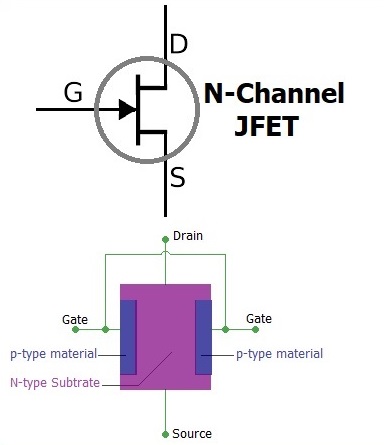

Fig. 1. JFET Construction, Working and Biasing

Steps to perform the real measurement in HP 4145B Semiconductor Parameter Analyzer

Equipment and Components

- n-channel JFET (e.g., 2N5457 or similar)

- DC power supply

- Digital multimeters

- Function generator (if available)

- Resistors (for limiting current and setting up the circuit)

- Breadboard and connecting wires

- Oscilloscope (optional, for advanced analysis)

Circuit Diagram

The experimental setup consists of a basic circuit to measure the output characteristics of the n-channel JFET. The circuit is as follows:

- Connect the source terminal of the JFET to the ground.

- Connect a variable DC power supply between the drain and source terminals, allowing control of the drain-source voltage (VDS).

- Insert a resistor (RD) in series with the drain terminal to limit the current and measure the drain current (ID) indirectly.

- Connect the gate terminal to another variable DC power supply to adjust the gate-source voltage (VGS).

Procedure

Setup the Circuit

Assemble the circuit on a breadboard as per the circuit diagram. Ensure all connections are secure and check the polarity of the power supplies.

Initial Calibration

- Set the gate-source voltage (VGS) to zero volts (VGS = 0V).

- Adjust the drain-source voltage (VDS) using the power supply and measure the corresponding drain current (ID) using a digital multimeter. Record the values.

Varying VDS

Incrementally increase VDS from 0V to a higher value (e.g., 20V) in small steps (e.g., 1V or 2V). For each VDS value, measure and record the corresponding ID.

Varying VGS

Repeat the above steps for different values of VGS (e.g., -1V, -2V, -3V). For each VGS value, vary VDS and record the corresponding ID.

Data Analysis

Plot the drain current (ID) versus drain-source voltage (VDS) for each value of gate-source voltage (VGS) on a graph. Identify the different regions of operation (ohmic, active, and cutoff regions) from the plotted curves.

Observations

- In the ohmic region, the ID increases linearly with VDS for small values of VDS, indicating that the JFET operates like a variable resistor.

- In the active region, the ID reaches a saturation point and becomes relatively independent of VDS, indicating the current saturation behavior of the JFET.

- In the cutoff region, for sufficiently negative VGS values, the ID approaches zero, indicating that the JFET is off.

Conclusion

From the experiment, the output characteristics of the n-channel JFET were successfully measured and analyzed. The ID vs. VDS curves for different VGS values provide insight into the device's behavior under varying conditions. The JFET's operation was observed in the ohmic, active, and cutoff regions, confirming the theoretical expectations.

Precautions

- Ensure the JFET is not exposed to excessive VDS or VGS to avoid damage.

- Use appropriate resistor values to limit the current and prevent overheating.

- Double-check all connections before powering the circuit to prevent short circuits or incorrect measurements.

Further Experiments

- Investigate the effect of temperature on the output characteristics of the n-channel JFET.

- Compare the output characteristics of different n-channel JFET models.

- Analyze the noise performance and input impedance variations with different operating points.